JPR-1ZI se od JPR-1Z liší tím že BOOT ROM má 8KB (2764) místo 2KB (2716) a obsahuje obvod (IO D4 7432 a D2 7400), co umožňuje zpracovat přerušení z obvodu 8259, obvod pro spolupráci Z80 s 8259 je převzat z PKT-1.

Z80 neumí spolupracovat s 8259 a to z toho důvodu že z 8259 je potřeba vyčíst 3 byte (instrukci CALL) a to pomocí signálu INTA jenomže Z80 v přerušovacím módu IM0 nevyčte pomoci „INTA“ z 8259 celou instrukci CALL aneb očekává instrukci RST, podle všeho Z80 vznikla dříve než 8259.

Pomocný obvod (IO D4A 7432 a D2B 7400) způsobí, že po příchodu signálu INTA přepne MR na INTA, při načítaní nové instrukce se pomocný obvod vrátí do výchozího stavu tj. MR je zase MR. Při použití přerušení s tímto pomocným obvodem musí být nastaven přerušovací režim u Z80 na IM2.

A celé to funguje následovně:

Na obsahu registru „I“ nezáleží, aneb se při přerušení neuplatní.

Po příchodu přerušení Z80 pomocí signálu INTA vyčte z 8259 byte a to konkrétně C9H což je instrukce CALL. Z pohledu Z80 je to nižší byt

adresy tabulky vektorů pro skok do přerušení.

Pomocný obvod přeplul signál MR na INTA.

Z registru „I“ si Z80 vyzvedne horní polovinu adres tabulky vektorů pro skok do přerušení a jde z paměti vyčíst adresu, na kterou se bude

skákat pro obsluhu přerušení. Jenomže Z80 nečte data z paměti ale z 8259 aneb pomocný obvod přesměroval MR na INTA aneb na adrese ze

které se Z80 snaží načíst adresu vektoru skoku, nezáleží.

Z80 má adresu kam skočí pro zpracování přerušení, aneb vnitřně provede obdobu instrukce CALL.

Pomocný obvod přeplul signál MR zpět na MR.

Z toho důvodu je nutno dodržet pravidla práci s přerušením v modu IM2 u Z80 aneb pro návrat z přerušení je nutno použit instrukci RETI

ale způsob jak je programově řešeno přerušení je velice podobné jak u 8080 s 8259. Ano je to takový kočko pes.

Zpátky na stromy, aneb po tom co jsem si pořádně prostudoval, jak vlastně funguje přerušení u INTELu (MCS80) a ZILOGu (Z80) tak jsem zjistil, že pěkně keckám z hladu ohledně programové obsluhy. Při tomto kočko psu, aneb Z80 oblbnutá aby pracovala s řadičem přerušení 8259(A) od INTELu, se nastaví mód přerušení na Z80 na IM2 ale zbytek obsluhy přerušení je potřeba řešit podle pravidel obsluhy 8259(A). K návratu z podprogramu přerušení stačí použít instrukci RET, instrukce RETI je nutná jen pro obvody z rodiny ZILOG.

Jak Z80 tak 8080A po příchodu (maskovatelného) přerušení zakážou přerušení, u obou CPU je potřeba znovu povolit přerušení pomocí instrukce EI. U obou CPU se povolí přerušení po příchodu instrukce EI až následníci instrukci tj. aby se stihla povést instrukce RET/RETI. Při ukončení obsluhy přerušení je potřeba zrušit i požadavek na obsluhu a to u rodiny obvodu Z80 pomoci instrukce RETI (periferní obvod který vyvolat přerušení čeká, až se na sběrnici objeví instrukce RETI a po příchodu instrukce RETI zruší požadavek k přerušení). U obvodu 8259(A) je to trošku složitější ale i u něj je potřeba povést zrušení požadavku na obsluhu a to že se do obvodu 8259(A) zapíše (instrukcí OUT) buď nespecifické či specifické zrušení požadavku přerušení (podle režimu přerušení).

Trik je v tom že Z80 se dostala k potřebné adrese, kam má skočit, aneb si vyčetla adresu z 8259(A) místo z RAM s přispěním obvodů rodiny ZILOG. Veškeré skoky na obsluh přerušení jak u Z80 tak 8080A jsou variace na instrukci CALL tj. skok do podprogramu. To jakým obvodem je řešeno přerušení CPU nepozná. Proto je potřeba dodržet pravidla obsluhy přerušení podle toho jaký obvod vyvolal přerušení tj. rodina obvodů Z80 nebo 8259(A).

Podle popisu jak vnitřně funguje 8080A se počítalo s tím, že pro přerušení se budou používat pouze instrukce RST, i vnitřní pochody v 8080A tomu nasvědčují (velmi podrobný popis 8080A je například v ST 12/1981). To že jde podstrčit při přerušení 8080A i instrukce CALL a vlastně jakákoliv instrukce je podle všeho jen nezamýšlená vlastnost. Zpracování instrukce během vykonávání kódu a během přerušení se liší jen v drobnostech. Při přerušení se zpracování instrukce liší jen v tom, že se zakáže přerušení, je zablokováno zvyšování programového čítače (registr PC) a instrukce je vyžádána pomocí signálu INTA místo MR, je proveden strojový cyklus M1I místo M1. Jinak se zpracování instrukce neliší od běžného zpracování. Instrukce RST jsou jedno bytové, ale CALL instrukce má 3 byty. Nějakým řízením osudu se případné strojové cykly M2 a M3 které obsahuji data či adresu načtou také pomocí INTA aneb místo strojových cyklů M2 a M3 se provedou strojové cykly M2I a M3I.

O takto podrobném popisu pro Z80 který je k 8080A nevím, ale z toho mála a toho kočko psa usuzuji, že chování módů u Z80 vypadá následovně. Že módy IM0 a IM1 se chovají přesně podle popisu pro 8080A aneb u módu IM0 se předpokládaná pouze a jedině instrukce RSTn u módu IM1 si CPU sám dosadí instrukci RST38. Mód IM2 vypadá na variaci Instrukce RST, spíše to bude naopak, kdy místo operačního kódu instrukce se načte dolní polovina adresy (horní polovina adresy je v registru „I“). Ve všech třech případech se načte první byte pomocí INTA (u IM1 je to vnitřní záležitost CPU). Instrukce RSTn nemají strojové cykly M2 a M3 ale dochází uvnitř CPU ke složení adresy z operačního kódu instrukce a skočí se na danou adresu. V módu IM2 nedošlo k načtení operačního kódu instrukce ale dolní poloviny adresy, vzhledem k tomu že v instrukcí RSTn je zakódovaná adresa tak jde jen o variaci na téma. CPU, složí adresu podle jiných pravidel než u instrukcí RSTn v módech IM0 a IM1 ale tentokrát provede standardní strojové cykly M2 a M3 kdy složená adresa poslouží k vyčtení adresy, kam se bude skákat.

Podle všeho toto bude ten důvod proč Z80 neumí přímo spolupracovat s 8259(A) aneb 8259(A) využívá vlastnosti 8080A které nejsou popsané v dokumentaci. Módy přerušení IM0 a IM1 byli doplněné spíše jen pro lepší přechod z 8080A na Z80. Módy přerušení IM0 a IM1 budou spíše odvozeninou z módu přerušení IM2 než naopak.

Při vzniku desky JPR-1Z se vloudila chyba při generování signálu STSTB. Chyba se projevu při použití mapování s

kartami, které generují WAIT typicky AND-1Z a DGD-1. Chyba se projevuje tak že se

nastaví WAIT, ale už z něj není cesty ven krom resetu. Stejná chyba je i na JPR-1ZI, oprava chyby generování STSTB se provede tak že na MKO

74123, který je zodpovědný za generování impulzu STSTB, se odpojí reset MKO od odporu R30 a připojí se signál /RFSH.

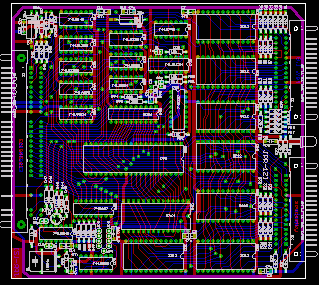

Seznam součástek

polovodiče

| 1 | D1A | 74LS14 |

| 3 | D1B, D4A, D5A | 74LS32 |

| 1 | D1C | 74LS74 |

| 2 | D2A, D3A | 74LS125 |

| 1 | D2B | 74LS00 |

| 1 | D2C | 74LS123 |

| 1 | D3B | 74LS08 |

| 2 | D3C, D6B | 74S287 |

| 1 | D6A | 74LS04 |

| 1 | D7B | 74LS93 |

| 7 | D5C, D1D - D6D | 3212 (MH3212, I3212, I8212, 74S412, ...) |

| 1 | D5B | Z80-CPU (UB880D, ...) |

| 1 | D4C | 2764 / 2864 |

| 1 | D2 | LED |

| 1 | V1 | KA206 |

| 1 | V2 | KSY81 |

Kondenzátory

| 1 | C1 | 1n | keramický |

| 1 | C2 | 12p | keramický |

| 2 | C3, C4 | 20u | elektrolytický |

| 11 | C5 - C15 | 47n | keramický |

| 1 | C16 | 10n | keramický |

| 1 | C17 | 33p | keramický |

odpory

| 28 | R1 - R18, R20 - R28, R41 | 4k7 |

| 2 | R19, R44 | 220 |

| 7 | R29, R30, R32 - R34, R36, R37 | 10k |

| 1 | R31 | 5k6 |

| 2 | R35, R38 | 100 |

| 4 | R39, R40, R42, R46 | 1k |

| 1 | R43 | 22 |

| 1 | R45 | 1k2 |

ostatní

| 1 | Q1 | 16MHz | krystal HC49 |

| 1 | X1 | TY 517 62 11 nebo TY 525 62 11 | klíč C6 |

| 1 | X2 | TY 513 30 11 nebo TY 527 30 11 | klíč F3 |

| 1 | X3 | TY 513 30 11 nebo TY 527 30 11 | klíč C6 |

| 1 | JP1 | dutinková lišta 1X1 | |

| 2 | JP2, JP3 | dutinková lišta 1X4 |

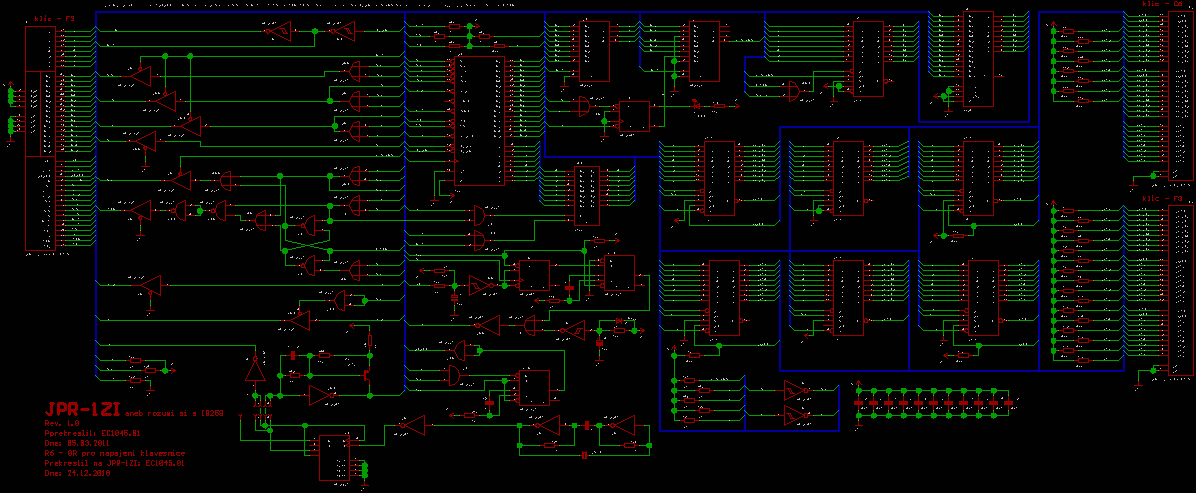

Schéma JPR-1ZI a černobílá verze ZDE.

Schéma JPR-1ZI opravy a černobílá verze ZDE.